CMOS technology, short for Complementary Metal Oxide Semiconductor, is a fundamental technology in the design and fabrication of integrated circuits (ICs). It plays a critical role in various electronic components, including microprocessors, batteries, and digital sensors. CMOS technology is known for its significant advantages, such as low power consumption and high integration density, making it the preferred choice in modern electronics.

Table of Contents

- 1. Definition of CMOS Technology

- 2. Historical Background

- 3. How CMOS Technology Works

- 4. Advantages of CMOS Technology

- 5. Applications of CMOS Technology

- 6. Disadvantages of CMOS Technology

- 7. The Future of CMOS Technology

- 8. FAQs

1. Definition of CMOS Technology

CMOS technology is a process technology used to fabricate integrated circuits. It utilizes complementary and symmetrical pairs of p-type and n-type MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors) for logic functions. The combination of these transistors enables CMOS to achieve lower static power dissipation compared to other technologies, such as NMOS or PMOS logic.

2. Historical Background

The development of CMOS technology dates back to the late 1960s. The first commercial CMOS device was introduced by RCA in 1968, paving the way for its widespread use in integrated circuits. Prior to CMOS, NMOS and PMOS technologies were the standards for logic gate fabrication. Although initially slower and more expensive than NMOS technology, CMOS eventually became the dominant technology due to its advantages in power consumption and scalability.

3. How CMOS Technology Works

CMOS technology utilizes both NMOS and PMOS transistors to create logic gates. In a typical CMOS inverter, for instance, when the input is low (logic 0), the PMOS transistor is activated, connecting the output to VDD (high voltage). Conversely, when the input is high (logic 1), the NMOS transistor conducts, connecting the output to ground (logic 0). This complementary operation allows for efficient switching and reduced power consumption.

NMOS

N-channel MOSFETs are made up of an

N-type source and drain that are diffused on a P-type substrate.

Electrons make up the vast majority of carriers. The NMOS will conduct

when the gate voltage is sufficiently high; otherwise, it will not. NMOS

is considered to be faster than PMOS since the majority of carriers

(electrons) travel faster than holes.

PMOS

A Source and Drain are also diffused on a substrate in P-channel MOSFETs. The source is of the P type, while the substrate is of the N type. The vast majority of carriers are voids. When a low voltage is provided, PMOS will conduct. The PMOS will not conduct if a high voltage is applied to the gate.

CMOS

As CMOS technology employs both N-type and P-type transistors in the creation of logic functions, a signal that turns on one transistor type is utilized to turn off the other. This replaces the need for pull-up resistors with simple switches. N-type MOSFETs are organized in a pull-down network between the output and the low voltage supply rail (VSS or ground) in CMOS logic gates, whereas P-type MOSFETs are positioned in a pull-up network between the output and the higher-voltage rail (typically VDD). As a result, when the P-type MOSFET is turned off, the N-type MOSFET is turned on, and vice versa. For any given input pattern, one of the networks is turned on and the other is turned off. High speed, low power dissipation, high noise margins in both states, and a wide range of source and input voltages (fixed source voltage) are all advantages of CMOS.

CMOS Logic Gates

CMOS technology enables the design of various logic gates, including:

- Inverter: The simplest form of CMOS gate that outputs the inverse of the input.

- NAND Gate: A gate that outputs low only when all its inputs are high.

- NOR Gate: A gate that outputs high only when all its inputs are low.

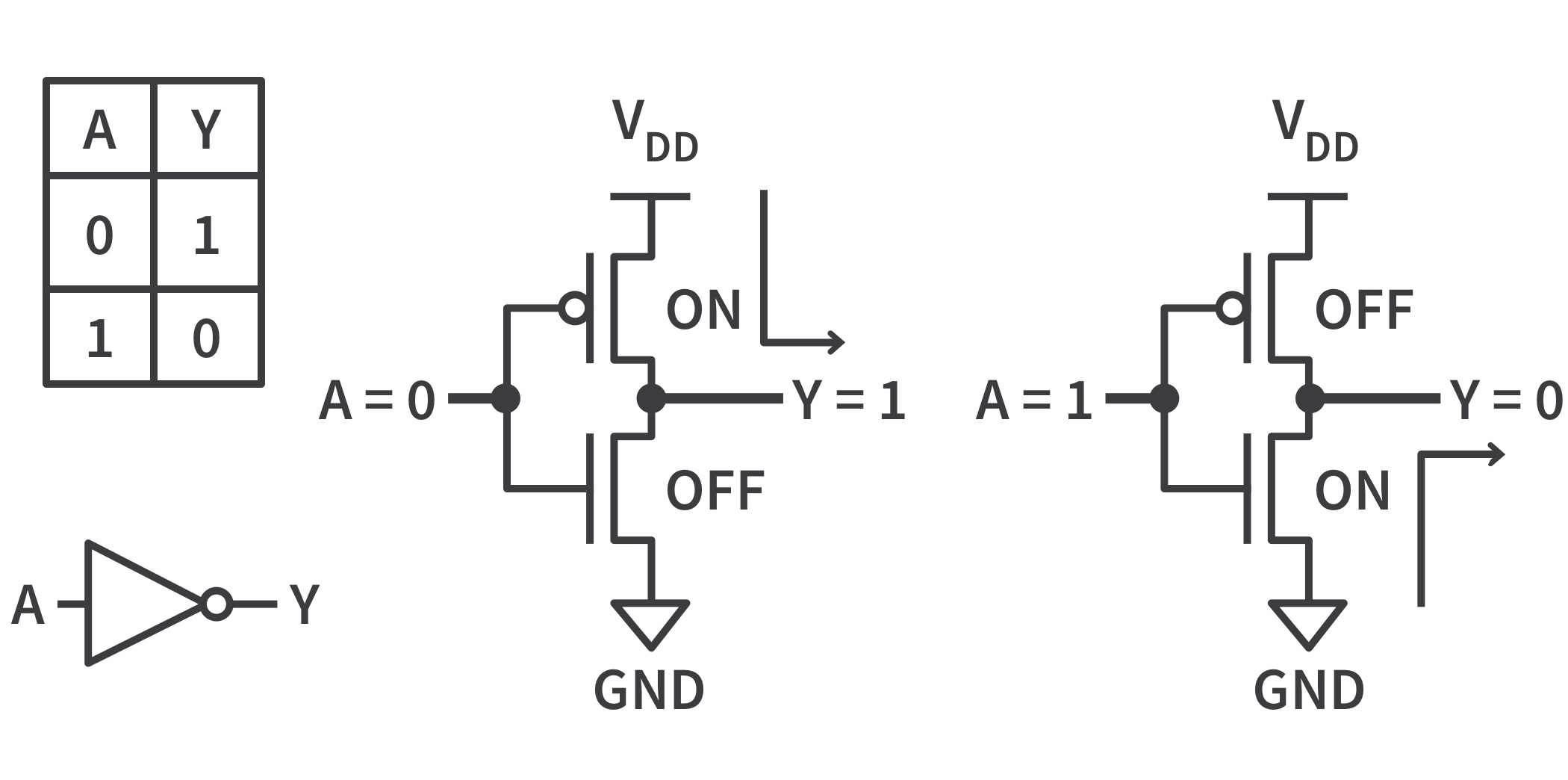

1) Inverter CMOS

The most basic CMOS logic gate is the inverter. The circuit is made up of PMOS and NMOS FETs. The gate voltage for both transistors is provided by input A, while the output is provided by Y.

The NMOS transistor is powered by VSS or ground, while the PMOS transistor is powered by VDD. When the input (A) is low (VDD, 0 V, Logic 0), the NMOS is turned off and the PMOS is turned on. VDD will be seen at the output via the P-channel MOSFET circuit. As a result, with the circuit pushed up to VDD, there is output (Logic 1). When the input is high (VDD, Logic 1), the PMOS is turned off and the NMOS is turned on. The output has been brought down and is hence low (Logic 0).

2) CMOS NAND Gate

Two N-channel MOSFETs are connected in series between Y (output) and

GND in a 2-input NAND gate, and two P-channel MOSFETs are connected in

parallel between VDD and Y

At least one of the NMOS transistors will be turned off if either A or B is low (Logic 0). Because the NMOS transistors are coupled in series, this interrupts the flow from Y to GND. In this situation, however, at least one of the PMOS transistors is turned on, completing the circuit from Y to VDD. This raises the output Y (Logic 1). For Y to be low, both A and B must be high in order for both NMOS transistors to be ON and the path from Y to GND to be complete. Y will be positive for all other input combinations. The NAND logic gate truth table is shown below.

3) CMOS NOR Gate

The NMOS transistors of a 2-input NOR gate are connected in parallel, whereas the PMOS transistors are connected in series. At least one NMOS transistor pulls the output low when at least one of the inputs is high. Only when both inputs are low is the output high.

The NOR logic gate truth table is shown below.

4. Advantages of CMOS Technology

CMOS technology offers several key advantages, including:

- Low Power Consumption: CMOS circuits draw significant power only during switching, resulting in lower static power dissipation.

- High Noise Immunity: CMOS technology exhibits high noise margins, making it robust against voltage fluctuations.

- High Density: The complementary nature of CMOS allows for greater integration density, enabling the fabrication of millions of transistors on a single chip.

- Scalability: As technology progresses, CMOS transistors can be scaled down to smaller dimensions, improving performance and efficiency.

5. Applications of CMOS Technology

CMOS technology is widely used across various applications, including:

- Microprocessors: The brains of computers and smartphones utilize CMOS technology for processing tasks efficiently.

- Image Sensors: CMOS image sensors are prevalent in digital cameras and smartphones due to their low power consumption and compact size.

- Memory Chips: Static RAM (SRAM) and dynamic RAM (DRAM) are commonly manufactured using CMOS technology.

- Radio-Frequency Identification (RFID): CMOS technology plays a significant role in the development of RFID tags, enabling efficient tracking and identification.

6. Disadvantages of CMOS Technology

Despite its advantages, CMOS technology has some limitations, including:

- Complex Manufacturing Process: The fabrication of CMOS circuits can be more complex than that of NMOS or PMOS due to the need for both types of transistors.

- Susceptibility to Radiation: CMOS devices can be more sensitive to radiation, making them less suitable for certain applications in space or high-radiation environments.

- Short Channel Effects: As transistors are scaled down, short channel effects can lead to performance degradation.

7. The Future of CMOS Technology

The future of CMOS technology looks promising, with ongoing advancements aimed at improving performance, efficiency, and integration. Research in new materials, such as graphene and carbon nanotubes, could further enhance the capabilities of CMOS technology. Additionally, as the demand for high-performance computing and mobile devices continues to rise, the development of ultra-low power CMOS technology will be crucial for sustaining growth in the semiconductor industry.

8. FAQs

Q1: What does CMOS stand for?

A: CMOS stands for Complementary Metal Oxide Semiconductor, a technology used for fabricating integrated circuits.

Q2: What are the main advantages of CMOS technology?

A: The main advantages of CMOS technology include low power consumption, high noise immunity, high integration density, and scalability.

Q3: Where is CMOS technology commonly used?

A: CMOS technology is widely used in microprocessors, image sensors, memory chips, and RFID systems.

Q4: What are the disadvantages of CMOS technology?

A: Some disadvantages include complex manufacturing processes, susceptibility to radiation, and short channel effects as transistors are scaled down.

Q5: How does a CMOS inverter work?

A: In a CMOS inverter, when the input is low (logic 0), the PMOS transistor turns on, connecting the output to VDD. When the input is high (logic 1), the NMOS transistor turns on, connecting the output to ground.